在现代高速数字电路和射频(RF)系统中,印刷电路板(PCB)上的传输线性能直接决定了整个系统的信号完整性(SI)与电源完整性(PI)。其中,三层板传输线(Triplate Stripline)作为一种重要的布线结构,因其优异的抗干扰性和可控的阻抗特性,被广泛应用于对噪声敏感的高性能设计中。然而,其性能并非在制板后就能自动保证,严谨的测试与验证是通往可靠产品的必经之路。

什么是三层板传输线?

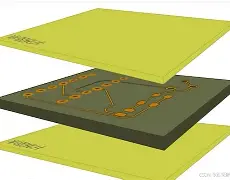

三层板传输线,是一种带状线(Stripline)结构。它由一条位于介质层中间的导带(信号线)和上下两个平行的参考层(通常为接地层)构成,信号被完全屏蔽在两层导体之间。这种结构使其具有以下特点:

- 出色的抗干扰能力: 外层参考层提供了天然的电磁屏蔽,极大减少了对外辐射和受外界干扰的风险。

- 稳定的阻抗控制: 介质环境对称,阻抗计算相对简单且易于在制造中控制。

- 较低的信号色散: 适用于高速、高频信号的传输。

为何必须进行专门测试?

即使设计理论完美,实际产品也会因介质材料偏差(Dk/Df)、制造工艺波动(线宽、介质厚度)、层压对准等因素而出现性能偏差。测试的核心目的,就是验证实际传输线是否达到设计的电气性能指标,并识别潜在缺陷。

关键测试参数一览

| 测试参数 | 说明 | 为什么重要 |

|---|---|---|

| 特征阻抗 | 传输线本身的瞬时电压与电流之比。 | 阻抗不匹配会导致信号反射,引起过冲、振铃,破坏信号质量。 |

| 插入损耗 | 信号在传输线中传播时的能量损失。 | 过高的损耗会导致信号幅度衰减,影响传输距离和接收端信噪比。 |

| 回波损耗 | 因阻抗不匹配而反射回来的信号能量。 | 直接衡量阻抗匹配的质量,回波损耗越差,反射越严重。 |

| 串扰 | 相邻传输线之间不期望的能量耦合。 | 近端和远端串扰会引入噪声,可能导致逻辑错误。 |

| 相位常数/传播延迟 | 信号沿传输线传播的速度。 | 对时序要求严格的系统(如差分对、并行总线)至关重要。 |

如何进行测试:方法与步骤

专业的测试通常依赖于矢量网络分析仪(VNA)和精心设计的测试结构(如测试耦合板、专用测试条)。

- 测试准备:

- 设计并制作包含特定传输线结构的测试板。

- 使用校准套件对VNA进行完整的校准(如SOLT、TRL),将参考面移至测试电缆末端。

- 连接与测量:

- 使用高精度射频电缆和连接器将测试板接入VNA。

- 设置合适的频率扫描范围(覆盖您的信号主要频率及谐波)。

- 分别测量S参数:S11(回波损耗)、S21(插入损耗)、S31/S41(串扰)等。

- 数据分析:

- 将测量得到的S参数数据导入仿真软件或专用分析工具。

- 通过TDR(时域反射计)功能分析阻抗一致性。

- 提取关键指标:阻抗值、损耗(dB/单位长度)、串扰峰值等,并与设计目标对比。

常见挑战与解决思路

- 去嵌入夹具效应: 测试夹具(连接器、焊盘)本身会影响结果,需使用仿真或算法将其影响去除,以得到纯粹传输线的性能。

- 谐振与模态耦合: 在特定频率,测试结构可能产生谐振,干扰真实测量。优化测试板设计和接地过孔布局可以缓解。

- 材料特性未知: 实际PCB板材的介电常数(Dk)和损耗角正切(Df)可能与标称值有偏差。可通过测量已知长度的传输线反推这些材料参数。

总结

三层板传输线的测试是连接理论设计与实际产品的一座关键桥梁。它通过客观数据揭示了制造引入的变异,确保信号在“不可见”的通道中能够完整、可靠地传输。从阻抗一致性到损耗评估,每一项测试都是对最终产品稳定性与可靠性的重要投资。在速率越来越高、集成度越来越大的电子时代,忽视这部分验证工作无异于在黑暗中冒险。

面对高频高速电路测试的复杂挑战,我司晟安电磁提供专业的信号完整性一站式测试与解决方案。我们拥有先进的矢量网络分析仪、实时示波器及完善的仿真软件平台,可为您提供:

- PCB传输线全参数测试(阻抗、S参数、TDR/TDT分析)

- 高速连接器与电缆组件性能评估

- 板级与系统级电源完整性(PI)测试

- 信号完整性仿真与实测数据对比验证服务 我们的专家团队能帮助您精准定位问题根源,从设计端到产品端,为您的硬件性能与可靠性保驾护航。欢迎随时联系我们,共同攻克技术难关。